# SEPT Operation Control And Data Processing Requirements

PREPARED BY L. DUVET AND H. SMIT

**VERSION 3.0**

**MAY 2003**

# TABLE OF CONTENTS

| 1   | OBJECTIVES                                  | 7  |

|-----|---------------------------------------------|----|

| 2   | REVISION HISTORY                            | 8  |

| 3   | APPLICABLE DOCUMENTS                        | g  |

| 4   | ACRONYMS AND ABBREVIATIONS                  | 9  |

| 5   | OVERVIEW                                    | 10 |

| 5.1 | Introduction                                | 10 |

| 5.2 | Block Diagram                               | 10 |

| 5.3 | Housekeeping                                | 12 |

| 6   | COMMUNICATION SPECIFICATIONS                | 13 |

| 6.1 | Asynchronous serial link                    | 13 |

| 6.2 | Interrupt line                              | 14 |

| 6.3 | Command structure: parameters and arguments | 14 |

| 6.4 |                                             |    |

| 6.5 | •                                           |    |

| 7   | INTERRUPT REGISTER                          | 15 |

| 8   | OPERATIONAL MODES                           | 17 |

| 8.1 | Settings Look Up Table                      | 17 |

| 8.2 | Accumulation time                           | 18 |

| 8.3 | Filtered event counters                     | 18 |

| 8.4 |                                             |    |

|     | Nominal Mode                                | 19 |

| 8.6 | Calibration Mode                            | 22 |

| 8.7 | Test Generator Mode                         | 24 |

| 8.8  | A alone mode                                     | . 29 |

|------|--------------------------------------------------|------|

| 8.9  | B alone mode                                     | . 31 |

| 8.10 | Commissioning mode                               | . 32 |

| 9 P  | RE/POST OPERATION SEQUENCES                      | 40   |

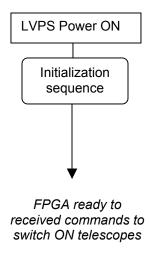

| 9.1  | Initialization sequence                          | . 40 |

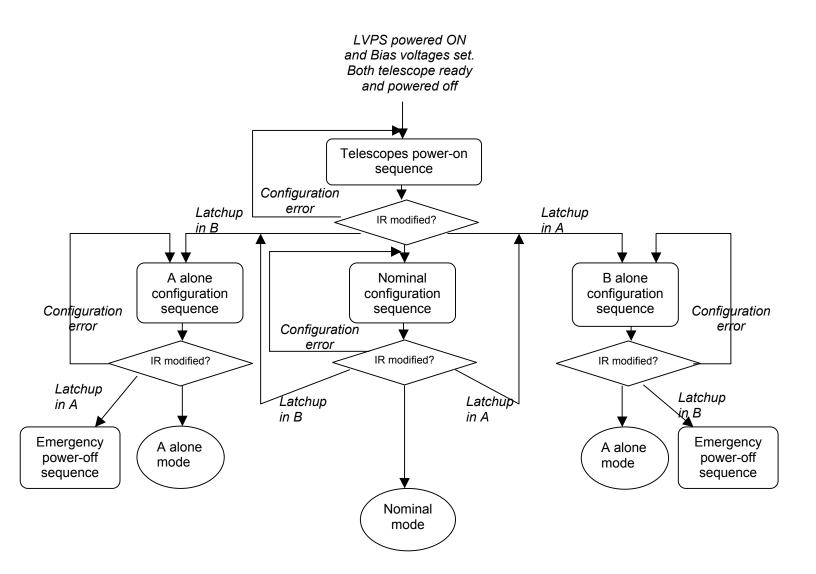

| 9.2  | Telescopes power-on sequence                     | . 40 |

| 9.3  | Nominal Configuration Sequence                   | . 41 |

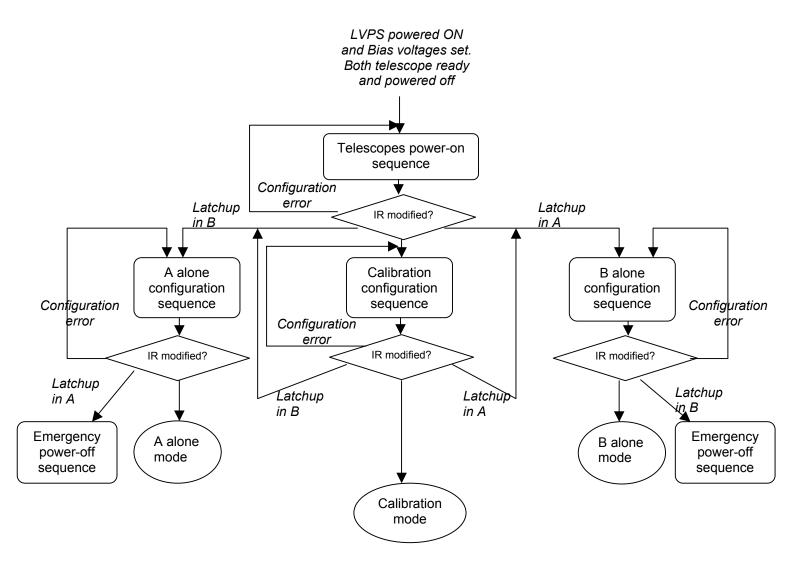

| 9.4  | Calibration Configuration Sequence               | . 42 |

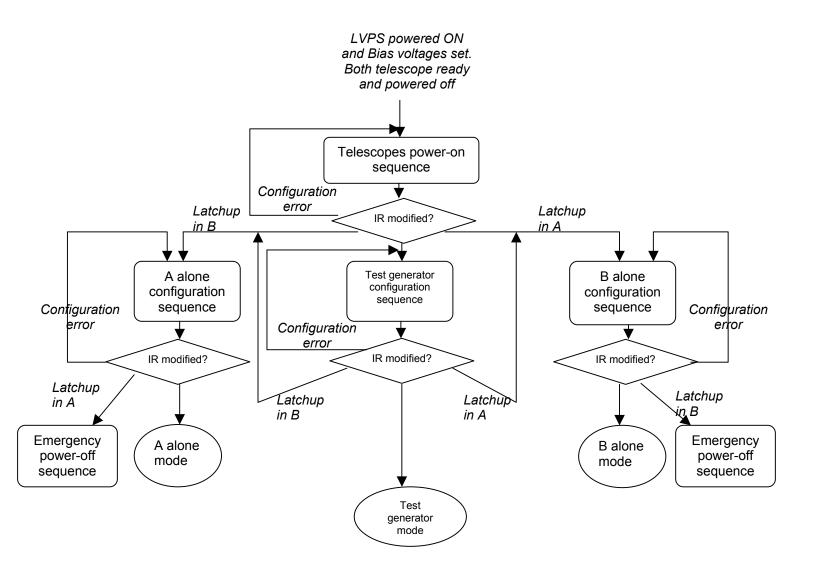

| 9.5  | Test Generator Configuration Sequence            | . 42 |

| 9.6  | A alone Power ON sequence                        | . 44 |

| 9.7  | B alone Power ON sequence                        | . 45 |

| 9.8  | A alone configuration sequence                   | . 45 |

| 9.9  | B alone configuration sequence                   | . 46 |

| 9.10 | Telescope A reset sequence                       | . 46 |

| 9.11 | Telescope B reset sequence                       | . 46 |

| 9.12 | Emergency power-off Sequence                     | . 47 |

| 9.13 | Telescopes power-off Sequence                    | . 47 |

| 10   | STATUS WORD                                      | 48   |

| 11   | INTERRUPT REGISTER MODIFICATIONS HANDLING        | 49   |

| 11.1 | Time stamp and priority                          | . 49 |

| 11.2 | Timer interrupt (bit 2 of the IR)                | . 49 |

| 11.3 | Counter Saturation (bit 3 or 4 of the IR)        | . 49 |

| 11.4 | PDFE configuration error (bit 8 to 11 of the IR) | . 49 |

| 11.5 | Latchup (Bit 12 to 15 of IR)                     |      |

| 11.5 | T C C C C C C C C C C C C C C C C C C C          |      |

| 11.5 |                                                  |      |

| 11.5 |                                                  |      |

| 11.5 | All other cases                                  | . 50 |

| 12   | SEP HEALTH MONITOR                               | 51   |

| 13                                   | INSTRUMENT OPERATION                              | . 52           |

|--------------------------------------|---------------------------------------------------|----------------|

| 13.1                                 | Instrument Power ON                               | . 52           |

| 13.2<br>13.2<br>13.2<br>13.2<br>13.2 | 2.2 Calibration mode                              | 53<br>54<br>55 |

| 13.3                                 | Communication error                               | . 56           |

| 13.4                                 | SEP health monitor                                | . 56           |

| 14                                   | DATA PROCESSING REQUIREMENTS                      | . 57           |

| 14.1                                 | Nominal mode/Calibration mode/Test generator mode | . 57           |

| 14.2                                 | Beacon mode                                       | . 57           |

| 15                                   | DATA RATE                                         | . 58           |

| 15.1                                 | Nominal mode                                      | . 58           |

| 15.2                                 | Calibration mode                                  | . 58           |

| 15.3                                 | Test generator mode                               | . 58           |

| 15.4                                 | Commisionning mode                                | . 58           |

| 15.5                                 | Beacon mode                                       | . 58           |

| 16                                   | TEMPERATURE FORMAT                                | . 59           |

| 17                                   | DIFFERENCES BETWEEN ENGINEERING MODEL AND FM      | . 60           |

| 18                                   | LIST OF MODES AND SEQUENCES                       | . 60           |

| 18.1                                 | Modes                                             | . 60           |

| 18.2                                 | Sequences                                         | . 60           |

| 19                                   | FPGA DETAILS                                      | . 61           |

| 19.1                                 | Command parameter definition                      | . 61           |

| 19.2                                 | Commands without arguments                        | . 61           |

| 19.3                                 | Commands with arguments                           | . 62           |

| 19.4                                 | FPGA 32 bin table                                 | . 62           |

| 19.5  | FPGA full datasheet                                                           | 63 |

|-------|-------------------------------------------------------------------------------|----|

|       |                                                                               |    |

|       |                                                                               |    |

|       | List of tables                                                                |    |

|       | 1: HOUSEKEEPING CHANNELS THAT WILL BE MEASURED.                               |    |

|       | 2: SERIAL COMMUNICATIONS SETTINGS                                             |    |

|       | 3 ASYNCHRONOUS BIT SERIAL DATA FORMAT                                         |    |

|       | 4 COMMUNICATION TROUBLESHOOTING RESPONSE                                      |    |

|       | 5 Status register                                                             |    |

|       | 6 LUT_SETTINGS                                                                |    |

|       | 7 LUT_BEACON                                                                  |    |

|       | 8 CCSDS Unsegmented Code - Time Field                                         |    |

|       | 9: NOMINAL MODE COMMAND/RESPONSE SERIES                                       |    |

|       | 10 Calibration mode sequence                                                  |    |

|       | 11 TEST GENERATOR MODE: TEST 1                                                |    |

| TABLE | 12 TEST GENERATOR MODE: TEST 2                                                | 25 |

|       | 13 A ALONE MODE SERIES OF COMMANDS                                            |    |

|       | 14 Com1a to Com1d command sequence                                            |    |

|       | 15: INITIALIZATION SEQUENCE                                                   |    |

|       | E 16; COMMAND SEQUENCE TO POWER-UP PDFE                                       |    |

|       | 17: Nominal configuration sequence                                            |    |

| TABLE | 18: Configuration sequence                                                    | 42 |

| TABLE | 19: TEST1 GENERATOR MODE CONFIGURATION SEQUENCE                               | 43 |

| TABLE | 20: TEST 2 CONFIGURATION SEQUENCE                                             | 44 |

| TABLE | 21 A ALONE POWER ON SEQUENCE                                                  | 45 |

| TABLE | 22 B ALONE POWER ON SEQUENCE                                                  | 45 |

| TABLE | 23 A ALONE CONFIGURATION SEQUENCE                                             | 45 |

| TABLE | 24 TELESCOPE A RESET SEQUENCE                                                 | 46 |

| TABLE | 25 TELESCOPE B RESET SEQUENCE                                                 | 46 |

| TABLE | 26 PDFE POWER-OFF SEQUENCE                                                    | 47 |

| TABLE | 27 BEACON MODE CHANNELS DEFINITION                                            | 57 |

| TABLE | 28 DATA RATE FOR THE NOMINAL MODE                                             | 58 |

| TABLE | 29 DATA RATE FOR THE BEACON MODE                                              | 58 |

| TABLE | 31 PRELIMINARY TEMPERATURE CALIBRATION FIGURES                                | 59 |

| TABLE | 32 LIST OF OPERATIONAL MODE IDENTIFIERS                                       | 60 |

| TABLE | 33 LIST OF PRE/POST OPERATION SEQUENCE IDENTIFIERS.                           | 60 |

| TABLE | 34 FPGA COMMANDS CONVENTION                                                   | 61 |

|       | 35 FPGA COMMANDS WITHOUT ARGUMENTS                                            |    |

| TABLE | 36 FPGA COMMANDS WITH ARGUMENTS                                               | 62 |

|       | 37 Exponential binning table                                                  |    |

|       |                                                                               |    |

|       | List of figures                                                               |    |

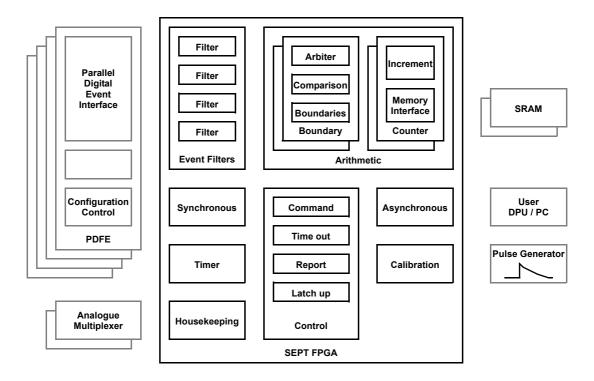

| Figur | E 1 SEPT BLOCK DIAGRAM                                                        | 11 |

|       | e 2 Serial link waveform format (at the connector level)                      |    |

|       | E 3 EXAMPLE OF WAVEFORM FOR THE ASYNCHRONOUS LINK AT THE SEPT CONNECTOR LEVEL |    |

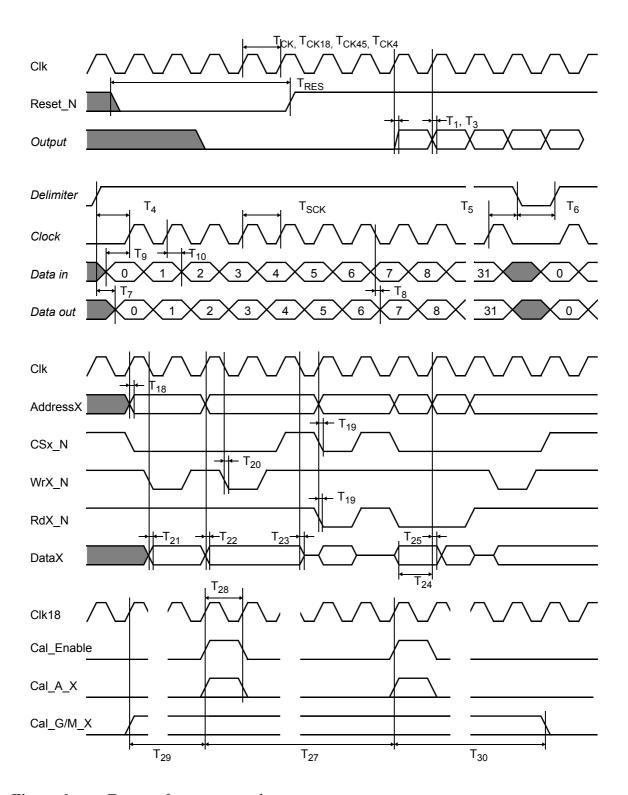

|       | E 4 TIMING DIAGRAM (NOT TO SCALE)                                             |    |

|       | E 5 TEST1A COMMAND SEQUENCE                                                   |    |

|       | E 6 TEST2A COMMAND SEQUENCE.                                                  |    |

|       | E 7 INSTRUMENT POWER-ON FLOW CHART                                            |    |

|       | E 8 NOMINAL OPERATION FLOW CHART                                              |    |

|       | E 9 CALIBRATION MODE OPERATION FLOW CHART                                     |    |

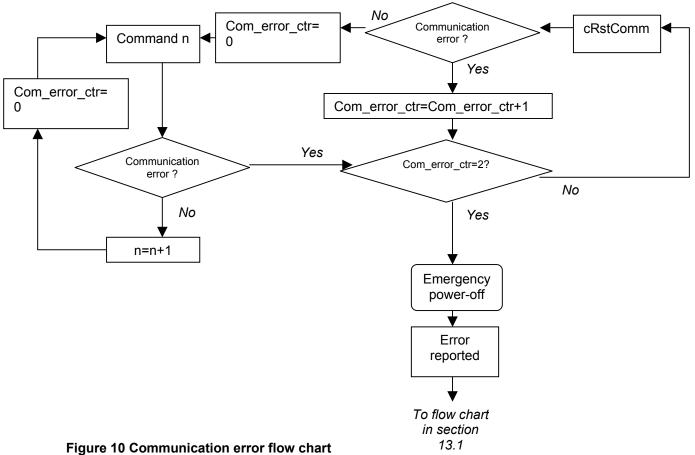

|       | E 10 COMMUNICATION ERROR FLOW CHART                                           |    |

|       | E 10 COMMUNICATION ERROR FLOW CHART                                           |    |

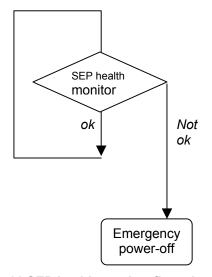

| LIGUN | LII DEI HEALIHWOMIOKILOW CHAKI                                                | 50 |

# 1 Objectives

The purpose of this document is to describe the foreseen operation control of the SEPT instrument by the SEP central processor. The document is based on the Engineering Model of the instrument. Some minor differences exist between the engineering model and the flight model, they will indicated accordingly in section 17.

Rem: to improve clarity, the present document should be printed in color.

# 2 Revision History

- Version 0.1 to 0.4: Sept-2002 Preliminary drafts.

- Version 0.5: Sept 2002- First release

- Version 1.0: Oct. 2002: includes comments of R. Mueller-Mellin +

- Spelling corrected

- Addition of Acronyms

- o Reaction to interrupts: separate section has been made to introduce the status word.

- Calibration mode detailed.

- Nominal mode detailed

- Detail on timing specifications

- o No separation between nominal mode and beacon mode at the command level.

- Look up table specifications updated.

- The use of the command cClearlrq has been reviewed in the pre/post operation sequence.

- Correction of the calibration configuration sequence (9.4)

- o Data processing requirement for nominal, calibration and test generator merged.

- o Binning indexes for the beacon mode.

- Version 1.1: Oct 2002

- Status word extended to contain operational mode designator

- last row changed to >2200.

- Version 2.0: November 2002

- o The document is now based on the EM FPGA (third prototype release)

- Details added

- All modes and sequences refined to reflect the agreement on the absence of instantaneous interrupt handling by the SEP-DPU

- Version 2.1: February 2003 (not released)

- Paragraph 6.1: asynchronous serial link waveform example added.

- Version 3.0: May 2003

- o Interruption table modified

- Single counter description updated

- Nominal mode updated

- Calibration mode description included

- o Test generator mode description included

- o Commissioning mode description included

- Initialization sequence updated

- cEnPDFE bit pattern corrected in telescope power on sequence, A alone power on sequence, B alone power on sequence.

- Test generator configuration sequence included

- o Bias voltage setting sequence A alone suppressed

- Bias voltage setting sequence B alone suppressed

- Status word updated

- Time stamp and priority section modified

- PDFE configuration error handling section modified

- SEP health monitor section updated

- Instrument power on flow chart modified

- Calibration mode flow chart updated

- Test generator flow chart updated

- Data rate for nominal rate updated

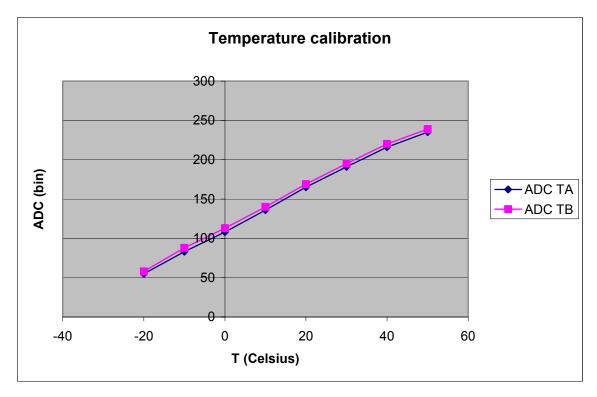

- Preliminary temperature sensor calibration curves (Engineering model) included,

8/63

Mode and sequence identifier table modified.

# 3 Applicable Documents

AD1 SEPT - FPGA Data Sheet – SEPT-001-04, version 1.2

AD2 RS-232 EIA/TIA Standard

AD3 Particle Detector Front End, Preliminary datasheet, IMEC, Nov. 28, 2000

AD4 CCSDS 301.0-B-2: Recommendation: Time Code Formats, Blue Book, Issue 2

# 4 Acronyms and Abbreviations

CS Center Segment (or main channel)

FPGA Field Programmable Gate Array

GR Guard Ring (or coincidence channel)

IR Interrupt Register LUT Look Up Table

PDFE Particle Detector Front End RAM Random Access Memory SEP Solar Energetic Particles

SEPT Solar Electron Proton Telescope

SSD Solid State Detector TBD To be defined TBC To be confirmed TBA To be added

# 5 Overview

# 5.1 Introduction

SEPT consists of two identical electronic units (SEPT-NS and SEPT-E) per STEREO spacecraft dedicated to the measurements of electrons (from 20 keV to 400keV) and ions (20 keV to 7 MeV). Each electronics unit analyses the signals of four solid-state detectors (SSD) and four corresponding guard rings. The four detectors are integrated in two opposite oriented telescopes, either in north-south (NS) or ecliptic (E) orientation. Each detector is connected to a PDFE (Particle Detector Front End) ASIC. Additional 9 housekeeping signals (+ 1 redundant) per unit are sampled and transferred to SEP-DPU as well as general status. A specific test generator permits control of the electronics in flight. The low-level operation of SEPT electronics is controlled by a specific FPGA. The high level operation of SEPT is controlled by the SEP central processor by means of commands sent on the serial interface. The same serial interface is used to transfer all scientific, calibration and housekeeping data from SEPT to SEP-DPU.

All the modes of operation of SEPT are based on a one-minute cycle.

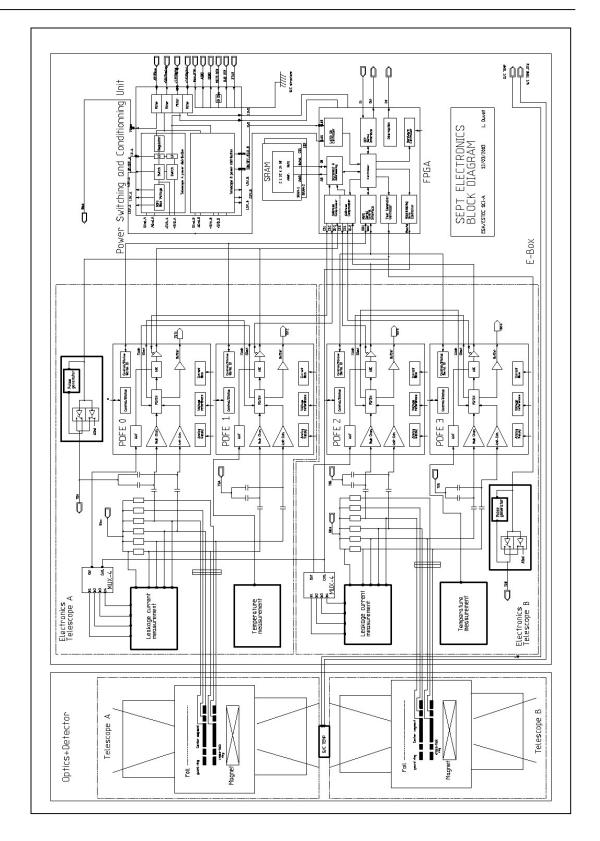

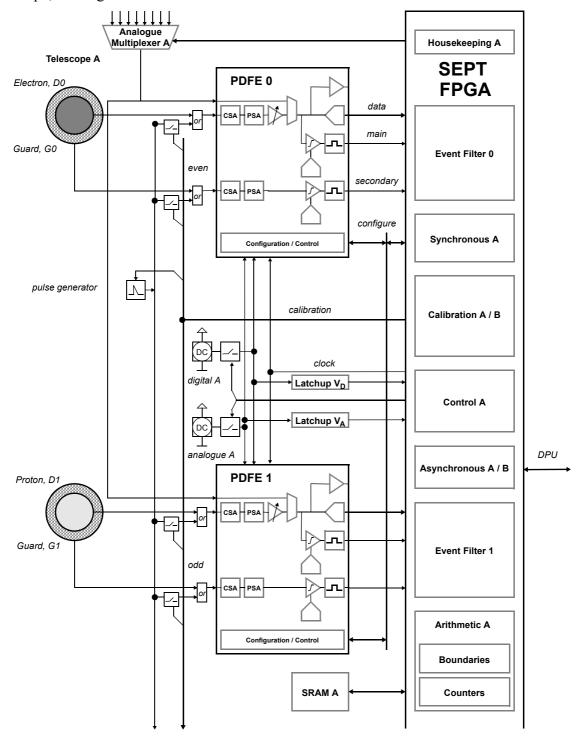

The block diagram in Figure 1 shows more details for one of the two SEPT telescope units (SEPT-NS and SEPT-E).

# 5.2 Block Diagram

One SEPT unit is divided into two telescopes (A and B), each telescope can be independently switched ON/OFF. In case of latchup in one telescope, only the corresponding telescope is automatically switched-off by the FPGA.

In addition to handling the detection of the charge particles impinging on the detectors, the PDFEs are also used to digitize the housekeeping:

- PDFE0: 4 leakage currents (related to the detectors of telescope A)

- PDFE 1: temperature TA (AD590: see section 16)

- PDFE 2: 4 leakage currents (related to the detectors of telescope B)

- PDFE 3: temperature TB (AD590: see section 16)

Only one of the two temperature sensor values shall be transmitted in the HK flow (by default TA). TB is only used when:

- An anomaly has been detected on the values of TA

- Telescope A is switched-off because of a latchup

Two RAMs (each being divided into 2 buffers) are used to store the recorded events (one per telescope).. However it has to be noted that these RAMs cannot store the events corresponding to two consecutive 1-minute measurement cycles. If unread, the data corresponding to the measurement cycle n are overwritten by the data corresponding to the cycle n+1, this feature means that a proper timing has to be defined between SEPT and SEP DPU to transfer the data. Indeed, during the transfer of the data, no event accumulation can take place, resulting in a "dead time" in the scientific acquisition". This dead time shall be minimized.

A counter placed in the FPGA is used to record all the events which occurred on a specific channel during a measurement.

Figure 1 SEPT Block diagram

# 5.3 Housekeeping

The following table lists the housekeeping channels in each SEPT unit<sup>1</sup>.

| Housekeeping Variable | Description                                       |

|-----------------------|---------------------------------------------------|

| HK_T                  | Temperature of the electronics                    |

| HK_CS0                | Leakage current of center segment linked to PDFE0 |

| HK_CS1                | Leakage current of center segment linked to PDFE1 |

| HK_CS2                | Leakage current of center segment linked to PDFE2 |

| HK_CS3                | Leakage current of center segment linked to PDFE3 |

| HK_GR0                | Leakage current of guard ring linked to PDFE0     |

| HK_GR1                | Leakage current of guard ring linked to PDFE1     |

| HK_GR2                | Leakage current of guard ring linked to PDFE2     |

| HK_GR3                | Leakage current of guard ring linked to PDFE3     |

Table 1: Housekeeping channels that will be measured.

HK\_T shall be used by the SEP central processor to control the operational heater (see remark on temperature in the introduction)

<u>Note</u>: the main channel of a PDFÉ is connected to the central segment (CS) of one detector; the coincidence channel is connected to the corresponding guard ring (GR).

<sup>&</sup>lt;sup>1</sup> A SEPT unit will always refer to SEPT-NS or SEPT-E

\_

# 6 Communication specifications

# 6.1 Asynchronous serial link

The communication between the SEPT instrument and the SEP central processor is made through an asynchronous serial link (compliant with AD2) with the parameters shown in Table 2, and Table 3.

| Setting   | Value |

|-----------|-------|

| Baud rate | 57600 |

| Start bit | 1     |

| Data bits | 8     |

| Stop bits | 2     |

**Table 2: Serial Communications settings**

The UART is built inside the SEPT FPGA. The bit rate for the transceiver is based on a 4.5 MHz internal clock (derived from the 18 MHz external clock).

The output rate is 57 692.3 baud (within 1.6% of 57600). This is derived by dividing 4.5 MHz with 78. On receipt, the FPGA can tolerate up to 10 % but this figure should be limited to 2 % to prevent potential errors.

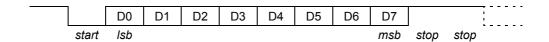

| Asynchronous RS232 type | start | D0    | D1    | D2    | D3    | D4    | D5    | D6    | D7    | Stop | Stop |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|

| format                  | first | LSB   |       |       |       |       |       |       | MSB   |      | last |

| General data            |       | 8*i+7 | 8*i+6 | 8*i+5 | 8*i+4 | 8*i+3 | 8*i+2 | 8*i+1 | 8*i   |      |      |

| format i={0,n}          |       | last  |       |       |       |       |       |       | first |      |      |

Table 3 Asynchronous bit serial data format

The table 3 defines the translation between the Asynchronous bit serial data format and the general data format used elsewhere in this document and in AD1. The Least significant bit is transmitted first.

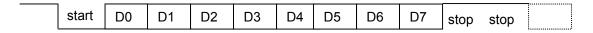

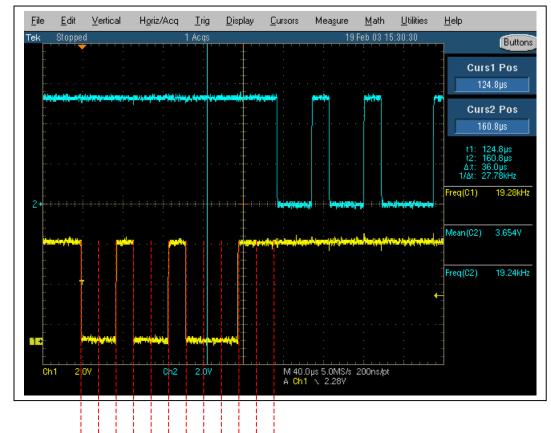

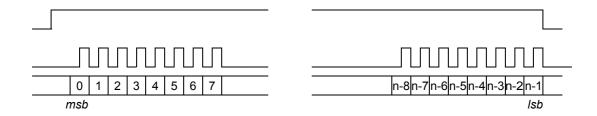

Ex: cClearIrq has the code 01110000 in the general data format (B0 to B7). The RS232 bits are sent in the D0 to D7 order as shown on Figure 2, besides in the case of cClear Irq, i=0 since 1 byte only is sent, then D0=B7, D1=B6....D7=B0. Consequently, the pattern 00001110 would be observed on the line with an oscilloscope (without the start and stop bits). The interface is independent of the transmitted data contents. No handshaking is required.

Figure 2 Serial link waveform format (at the connector level)

Positive logic is used. To avoid any ambiguity, the following figure show one particular example of waveforms measured at the SEPT connector.

CRstComm Command (00010010)

Figure 3 Example of waveform for the asynchronous link at the SEPT connector level.

stop stop

# 6.2 Interrupt line

start

A direct digital line exists between the SEPT instrument and the SEP processor (SEPT-E-LATCHUP and SEPT-NS-LATCHUP). This line is used for interrupt notification (see section 11) but will not be used for the interface with SEP DPU.

# 6.3 Command structure: parameters and arguments

01001000

All commands consist of an 8-bit pattern. Up to 3 bits in this pattern can be used as **parameters**, for addressing purposes (PDFE or telescope) and configuration. When a command consists only of a single byte, it is said to have no arguments. Some commands, such as cConfPDFE, have **arguments**. These arguments consist of one or several bytes sent after the 8-bit pattern command. It is assumed that there is at most 1.8 ms between the receipt of a command byte and subsequent argument on the input interface, otherwise a time-out response (rTimeOut, see appendix A) will be generated and the transmission will be aborted.

A command response always contains the command itself. This feature enables to check that the SEPT FPGA has properly received the command. Consequently, before the next command is

sent in a command sequence, the SEP processor shall always check that the previous command has been properly echoed. In the case of a non-properly echoed command the action to be taken is described in section 6.5. The structure of the response to a command depends on the command itself, detailed specifications for each command can be found in appendix 19.5. Unless specifically required, only the length of the response should be checked and not the content.

# 6.4 BREAK response

In addition to transmitting and receiving bytes, the serial interface can also generate a break code on the occurrence of an interrupt (see section 11). This is done by transmitting a zero start bit, one byte with the data filled all zero, two stop bits being zero and an additional zero bit to violate the nominal protocol.

The break signal is sent nearly simultaneously with the assertion of the external interrupt signal, only delayed by any ongoing byte transmission.

The SEP DPU should ignore the BREAK signal.

# 6.5 Communication errors

The following table lists the response issued by the SEPT FPGA whenever a problem occurs at the communication level.

| rUnknown | Send back 00000011  |  |

|----------|---------------------|--|

|          | whenever an unknown |  |

|          | command is sent     |  |

| rTimeOut | Send back 00001111  |  |

|          | whenever a time out |  |

|          | has occurred while  |  |

|          | waiting for an      |  |

|          | argument.           |  |

**Table 4 Communication troubleshooting response**

Whenever a rUnknown and rTimeOut or a non-properly echoed command is encountered by the SEP DPU, the cRstComm should be sent to reset the communication and the last command should be sent again. This operation can be repeated 1 more time. If after these 2 attempts, the problem is still present, the emergency switch-off sequence should be applied followed by the initialization sequence so that the current operation can be reestablished **automatically**. A maximum of two reboot for communication error should be tolerated everyday. The error should be reported only if the communication error has not been solved.

# 7 Interrupt register

The status of the instrument can be described by a certain number of bits contained in the interrupt register of the SEPT FPGA:

| Bit 0 Event propagation enabled on PDFE 0 and 1 (set to 1 when PDFE operational) |                                                 |  |  |

|----------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| Bit 1 Event propagation enabled on PDFE 2 and 3 (set to 1 when PDFE operation    |                                                 |  |  |

| Bit 2 Time Alarm interrupt, latched                                              |                                                 |  |  |

| Bit 3                                                                            | Saturation interrupt on PDFE 0 and 1, latched   |  |  |

| Bit 4 Saturation interrupt on PDFE 2 and 3, latched                              |                                                 |  |  |

| Bit 5 Not used                                                                   |                                                 |  |  |

| Bit 6                                                                            | PDFE 0 or 1 error or latchup during measurement |  |  |

| Bit 7 PDFE 2 or 3 error or latchup during measurement                            |                                                 |  |  |

| Bit 8 PDFE 0 configuration error, latched                                        |                                                 |  |  |

| Bit 9                                      | PDFE 1 configuration error, latched   |  |  |

|--------------------------------------------|---------------------------------------|--|--|

| Bit 10 PDFE 2 configuration error, latched |                                       |  |  |

| Bit 11                                     | PDFE 3 configuration error, latched   |  |  |

| Bit 12                                     | PDFE 0 or 1 analogue latchup, latched |  |  |

| Bit 13                                     | PDFE 0 or 1 digital latchup, latched  |  |  |

| Bit 14                                     | PDFE 2 or 3 analogue latchup, latched |  |  |

| Bit 15                                     | PDFE 2 or 3 digital latchup, latched  |  |  |

Table 5 Status register

Bits 2 to 15 are set to 1 whenever the corresponding event has happened. Bit 0 and bit 1 are set to 1 when the corresponding pair of PDFE is operational.

The whole register is accessible through the <code>cClearIrq</code> command. This command also clears all the latched interruption bits in the interrupt register.

Note: The cStatPDFE command gives access to the current PDFE status bits (from bit 8 to bit 15) unlatched, however this command will not be used.

# 8 Operational modes

# 8.1 Settings Look Up Table

A lookup table should be stored in the mass memory of the SEP processor. It shall contain all settings needed to properly operate the SEPT instrument and the binning parameters for the beacon mode (see 14.2). The LUT can be divided into two parts:

- LUT\_SETTINGS

- LUT BEACON

The following settings are needed (see AD3 for more details):

| Name              | Description                                     | Size   |

|-------------------|-------------------------------------------------|--------|

|                   |                                                 | (bits) |

| ACC_TIME          | Accumulation time                               | 24     |

| G_PDFE0-SEPT-E    | Conversion gain adjustment PDFE0-SEPT-E         | 5      |

| G_PDFE1-SEPT-E    | Conversion gain adjustment PDFE1-SEPT-E         | 5      |

| G_PDFE2-SEPT-E    | Conversion gain adjustment PDFE2-SEPT-E         | 5      |

| G_PDFE3-SEPT-E    | Conversion gain adjustment PDFE3-SEPT-E         | 5      |

| G_PDFE0-SEPT-NS   | Conversion gain adjustment PDFE0-SEPT-NS        | 5      |

| G_PDFE1-SEPT-NS   | Conversion gain adjustment PDFE1-SEPT-NS        | 5      |

| G_PDFE2-SEPT-NS   | Conversion gain adjustment PDFE2-SEPT-NS        | 5      |

| G_PDFE3-SEPT-NS   | Conversion gain adjustment PDFE3-SEPT-NS        | 5      |

| ML_PDFE0-SEPT-E   | Main event detection level PDFE0-SEPT-E         | 8      |

| ML_PDFE1-SEPT-E   | Main event detection level PDFE1-SEPT-E         | 8      |

| ML_PDFE2-SEPT-E   | Main event detection level PDFE2-SEPT-E         | 8      |

| ML_PDFE3-SEPT-E   | Main event detection level PDFE3-SEPT-E         | 8      |

| ML_ PDFE0-SEPT-NS | Main event detection level PDFE0-SEPT-NS        | 8      |

| ML_ PDFE1-SEPT-NS | Main event detection level PDFE1-SEPT-NS        | 8      |

| ML_ PDFE2-SEPT-NS | Main event detection level PDFE2-SEPT-NS        | 8      |

| ML_PDFE3-SEPT-NS  | Main event detection level PDFE3-SEPT-NS        | 8      |

| CL_PDFE0-SEPT-E   | Coincidence event detection level PDFE0-SEPT-E  | 8      |

| CL_ PDFE1-SEPT-E  | Coincidence event detection level PDFE1-SEPT-E  | 8      |

| CL_ PDFE2-SEPT-E  | Coincidence event detection level PDFE2-SEPT-E  | 8      |

| CL_ PDFE3-SEPT-E  | Coincidence event detection level PDFE3-SEPT-E  | 8      |

| CL_ PDFE0-SEPT-NS | Coincidence event detection level PDFE0-SEPT-NS | 8      |

| CL_ PDFE1-SEPT-NS | Coincidence event detection level PDFE1-SEPT-NS | 8      |

| CL_ PDFE2-SEPT-NS | Coincidence event detection level PDFE2-SEPT-NS | 8      |

| CL_ PDFE3-SEPT-NS | Coincidence event detection level PDFE3-SEPT-NS | 8      |

Table 6 LUT\_SETTINGS

The values stored in the LUT\_SETTINGS will be used by the cConfPDFE and cSetTimer commands.

The LUT\_BEACON shall contain the binning parameters for the beacon mode. The binning parameters are related to Table 27 and should be stored as 5 bit values with the following naming.

| Name          | Default value |

|---------------|---------------|

| Electron_bin1 | 1             |

| Electron_bin2 | 5             |

| Electron_bin3 | 8             |

| Electron_bin4 | 13            |

| Electron_bin5 | 17            |

| lon_bin1      | 1             |

| lon_bin2      | 8             |

| lon_bin3      | 20            |

| lon_bin4      | 30            |

| lon_bin5      | 31            |

Table 7 LUT\_BEACON

The lookup table shall be able to be modified by tele-commands from ground control.

The size of the LUT\_SETTINGS is 192 bits; the size of the LUT\_BEACON is 50 bits. The whole LUT is consequently 242 bits long.

There is one LUT\_setting per SEPT unit (E or NS), and a single LUT\_BEAQCON for all SEPT units.

# 8.2 Accumulation time

The SEP DPU shall know the actual accumulation time. The format used is compliant to the Time Field (T-Field) of the CCSDS Unsegmented Code, defined in AD4. The T-Field consists of two octets of coarse time (seconds) and one octet of fine time (sub seconds). The single fine time octet provides a resolution of 3.90 milliseconds.

| CCSDS Unsegmented Code       | Coarse                           | time        | Fine time                         |

|------------------------------|----------------------------------|-------------|-----------------------------------|

| <ul><li>Time Field</li></ul> |                                  |             |                                   |

| Bit weight                   | 2 <sup>15</sup> - 2 <sup>8</sup> | $2^7 - 2^0$ | 2 <sup>-1</sup> - 2 <sup>-8</sup> |

| Bit numbering                | 0-7                              | 8 - 15      | 16 –23                            |

| Rs232 type correspondence    | D7 – D0                          | D7 – D0     | D7 – D0                           |

# Table 8 CCSDS Unsegmented Code - Time Field

<u>Note</u>: The counter in the timer is based on a synthesizer to generate an internal binary clock frequency. The obtained synthesized frequency with a 32 bit wide frequency synthesizer is  $f_{\text{synth}}$  obtained = $f_{\text{ck}}^*$ 244335/ $2^{32}$ . The resulting static drift caused by the ratio between the ideal and obtained synthesized frequency is 225 microseconds per minute.

# 8.3 Filtered event counters

These counters are recording the filtered event for each detector, they are 24 bits wide, there are 4 of them located in two RAMs. The most significant byte (bits 0 to 7) of a counter is transmitted first over the asynchronous serial interface. In case of the 24 bit counters, the 31st counter is sent first, counter 0 is the most significant and counter 31 is the least significant.

# 8.4 Single Counter

The Single event counter records all the events associated to one channel during ACC\_TIME. It is 24 bits<sup>2</sup> wide which enables to cover 60 seconds at maximum count rate (250 kevents/s). Bits B0 to B7 are the most significant.

<sup>&</sup>lt;sup>2</sup> In the Engineering Model, the single counter is 23 bits wide only.

# 8.5 Nominal Mode

#### 8.5.1 Description

This mode will be used most of the time during the mission. It consists of the accumulation of the 4 buffers (per SEPT subsystem) during ACC TIME and the reading of the buffers, the PDFE working in full anti-coincidence mode. HK values will also be read at the end of each accumulation.

The accumulation duration is based on the internal timer of the FPGA. The binning of the energy is logarithmic and is done internally (32 bins) according to Table 37.

The nominal mode is an "endless" repetition of the 8 series of commands described in Table 9. The 8 series enable to cover the 8 channels (4 PDFE, main and coincidence channels) with the unique single counter (see paragraph 1.1.1).

It is assumed that the "Nominal Configuration sequence" described in section 9.3 has been initially performed.

The following table describes the series of commands and events in the case where no error occurs (else refer to section 11).

| Nom1 |               |                                                                                                                 |                                                                                                                |

|------|---------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| step | Command       | Bit pattern +arguments                                                                                          | Response (+ received command)                                                                                  |

| 1    | cStartRun     | 01100100                                                                                                        |                                                                                                                |

| 2    | cClearIrq cor |                                                                                                                 | E. During this period, SEP send the register (to check for latchup and y is discussed in 8.5.2).               |

| 3    | cClearIrq     |                                                                                                                 | Interrupt register with Bit 2 set to 1= timer interrupt                                                        |

| 4    | Cread32       | 10110000                                                                                                        | PDFE 0 32 counters                                                                                             |

| 5    | Cread32       | 10110001                                                                                                        | PDFE 1 32 counters                                                                                             |

| 6    | Cread32       | 10110010                                                                                                        | PDFE 2 32 counters                                                                                             |

| 7    | Cread32       | 10110011                                                                                                        | PDFE 3 32 counters                                                                                             |

| 8    | cConfPDFE     | 10010000+First byte:110xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ PDFE0-SEPT-E Third byte: CL_ PDFE0- SEPT-E | Configure PDFE 0 in ADC mode                                                                                   |

| 9    | cGetHK        | 01000000                                                                                                        | HK_CS0 (1 byte), HK_GR0 (1 byte), HK_CS1 (1 byte), HK_GR1 (1 byte)                                             |

| 10   | cConfPDFE     | 10010000+First byte:100xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ PDFE0-SEPT-E Third byte: CL_ PDFE0- SEPT-E | Configure PDFE0 back into the charge amplification mode with active coincidence channel (full anticoincidence) |

| 11   | cConfPDFE     | 10010001+First<br>byte:110xxxxx (xxxxx=<br>G_ PDFE1-SEPT-E                                                      | Configure PDFE 1 in ADC mode                                                                                   |

| (4<br>one                       |

|---------------------------------|

| the<br>vith<br>(full            |

| e                               |

| (1<br>3R3                       |

| the<br>vith<br>(full            |

| e                               |

| (4<br>one                       |

| the<br>vith<br>(full            |

| the<br>to<br>the<br>tion<br>for |

|                                 |

|                                 |

# Nom2

Same as Nom 1 except for step 20 which corresponds to the command 01001001: selection of single counter for PDFE1, main channel and read of single counter corresponding to PDFE0 coincidence channel.

#### Nom3

Same as Nom 1 except for step 20 which corresponds to the command01001101: selection single counter for PDFE1, coincidence channel and read of single counter corresponding to PDFE1, main channel

#### Nom 4

Same as Nom 1 except for step 20 which corresponds to the command01001010: selection of the single counter for PDFE2, main channel and read of single counter for PDFE1, coincidence channel

#### Nom 5

Same as Nom 1 except for step 20 which corresponds to the command01001110: selection of the single counter for the PDFE2, coincidence channel and read of single counter for the PDFE2 main channel

#### Nom 6

Same as Nom 1 except for step 20 which corresponds to the command 01001011: selection of the single counter for the PDFE3, main channel and read of single counter for PDFE2 coincidence channel

#### Nom 7

Same as Nom 1 except for step 20 which corresponds to the command 0100111: selection of the single counter for the PDFE3, coincidence channel and read of single counter for PDFE3 main channel.

#### Nom 8

Same as Nom 1 except for step 20 which corresponds to the command 0100000: selection of the single counter for PDFE0, main channel and read of single counter for PDFE3 coincidence channel

#### Table 9: Nominal mode command/response series

Step 8, 11, 14 and 17 configure the corresponding PDFE in ADC mode, steps 10, 13, 16 and 19 put them back in observation mode. This means that from one series to the next one, both telescopes are by default completely reconfigured.

TA and TB are acquired but only TA is transmitted in the HK flow and used for operational heater. The benefit of still acquiring both temperature is that the whole nominal sequence of commands stay the same even if one temperature sensor has failed. SEP should be able to choose one of the two values (TA by default) via a command from grounds.

Important: step 3 has to be carried out, i.e it has to be verified that the timer interrupt (bit 2) bit is set to 1.

Rem: The command corresponding to the single counter sends back the data corresponding to the targeted channel specified in the previous single counter command.

<u>Note:</u> the so called « beacon mode » corresponds to a special binning performed by the SEP processor and is based on the data produced in the nominal mode.

# 8.5.2 *Timing*

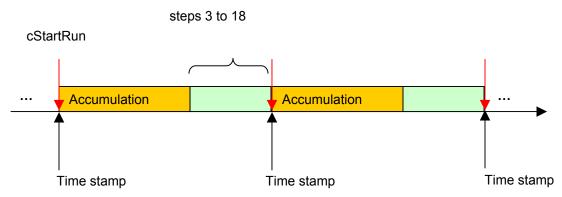

We detail here the timing for one series of steps. The main constraint is to start an accumulation (step 1) every 60 seconds (the start should be synchrone<sup>3</sup> with respect to the other SEPT units and if possible with respect to the other instruments of IMPACT (TBC Impact team). Since the time between two starts is fixed and the dead time should be as short as possible for scientific reasons, steps 3 to 20 should be performed as fast as possible. A rough estimate (considering

21/63

\_

<sup>&</sup>lt;sup>3</sup> A difference of a few milliseconds could be tolerated providing that it is fixed (in case the UART is common to two SEPT units)

the immediate response to a command) shows that the minimum time to carry out the different steps is around 100 ms, **300 ms** would be considered as a satisfying dead time, providing also margin enough to treat potential errors which may have occurred (especially PDFE configuration error, see section 11.4).

To limit the switching noise due to the interface, the polling frequency during the accumulation shall be limited to 0.2 Hz (THIS REMARKS APPLIES TO ALL THE OPERATION MODE). Since ACC\_TIME is known by SEP DPU, step 3 could be performed right after ACC\_TIME has been elapsed.

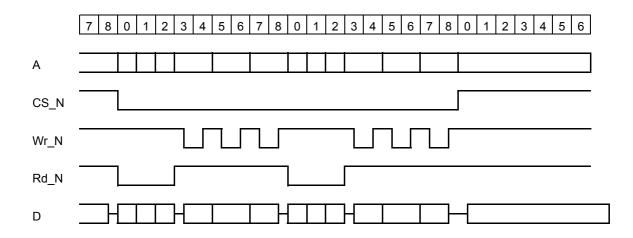

Figure 4 Timing diagram (not to scale)

# 8.6 Calibration Mode

This mode occurs once a month during one day. The difference with the previous mode resides only in the configuration of the instrument, which will be set to coincidence mode between two center segments of a telescope and in anticoincidence with the corresponding guard rings. Only the penetrating particles will be recorded.

Once the "calibration configuration" sequence has been carried out, Table 10 should be used as the definition of sequence of commands for the calibration mode.

The calibration mode is only valid when the telescopes are both powered on.

| Calib 1 |               |                                                                      |                                                                                                  |

|---------|---------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| step    | Command       | Bit pattern +arguments                                               | Response (+ received command)                                                                    |

| 1       | cStartRun     | 01100100                                                             |                                                                                                  |

| 2       | cClearIrq con |                                                                      | E. During this period, SEP send the register (to check for latchup and y is discussed in 8.5.2). |

| 3       | cClearIrq     |                                                                      | Interrupt register with Bit 2 set to 1= timer interrupt                                          |

| 4       | Cread32       | 10110000                                                             | PDFE 0 32 counters                                                                               |

| 5       | Cread32       | 10110001                                                             | PDFE 1 32 counters                                                                               |

| 6       | Cread32       | 10110010                                                             | PDFE 2 32 counters                                                                               |

| 7       | Cread32       | 10110011                                                             | PDFE 3 32 counters                                                                               |

| 8       | cConfPDFE     | 10010000+First byte:110xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ | Configure PDFE0 in ADC mode                                                                      |

|    |                  | PDFE0-SEPT-E                                                                                                                                     |                                                                                                                                                               |

|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                  | Third byte: CL_ PDFE0-<br>SEPT-E                                                                                                                 |                                                                                                                                                               |

| 9  | cGetHK           | 01000000                                                                                                                                         | HK_CS0 (1 byte), HK_GR0 (1 byte), HK_CS1 (1 byte), HK_GR1 (1 byte)                                                                                            |

| 10 | cConfPDFE        | 10010000+First byte:101xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ PDFE0-SEPT-E Third byte: CL_ PDFE0- SEPT-E                                  | Configure PDFE0 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard) |

| 11 | cConfPDFE        | 10010001+First byte:110xxxxx (xxxxx= G_ PDFE1-SEPT-E Second byte: ML_ PDFE1-SEPT-E Third byte: CL_ PDFE1- SEPT-E                                 | Configure PDFE1 in ADC mode                                                                                                                                   |

| 12 | cGetHK           | 01000001                                                                                                                                         | The temperature TA is read (4 times the same values), only one is taken for HK_T                                                                              |

| 13 | cConfPDFE        | 10010001+First byte:101xxxxx (xxxxx= G_ PDFE1-SEPT-E Second byte: ML_ PDFE1-SEPT-E Third byte: CL_ PDFE1- SEPT-E                                 | Configure PDFE1 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard) |

| 14 | cConfPDFE        | 10010010+First byte:110xxxxx (xxxxx= G_PDFE2-SEPT-E Second byte: ML_ PDFE2-SEPT-E Third byte: CL_ PDFE2- SEPT-E                                  | Configure PDFE2 in ADC mode                                                                                                                                   |

| 15 | cGetHK           | 01000010                                                                                                                                         | HK_CS2 (1 byte), HK_GR2 (1 byte), HK_CS3 (1 byte), HK_GR3 (1 byte)                                                                                            |

| 16 | cConfPDFE        | 10010001+First byte:101xxxxx (xxxxx= G_PDFE2-SEPT-E Second byte: ML_ PDFE2-SEPT-E Third byte: CL_ PDFE2- SEPT-E                                  | Configure PDFE2 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard) |

| 17 | cConfPDFE cGetHK | 10010011+ First byte:<br>110xxxxx (xxxxx= G_<br>PDFE3-SEPT-E<br>Second byte: ML_<br>PDFE3-SEPT-E<br>Third byte: CL_ PDFE3-<br>SEPT-E<br>01000011 | Configure PDFE3 in ADC mode  The temperature TB is read (4)                                                                                                   |

| 10 | COCII IN         | 01000011                                                                                                                                         | The temperature TB is read (4                                                                                                                                 |

|    |            |                                                                                                                   | times the same values), only one                                                                                                                                                      |

|----|------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | cConfPDFE  | 10010011+ First byte: 101xxxxx (xxxxx= G_ PDFE3-SEPT-E Second byte: ML_ PDFE3-SEPT-E Third byte: CL_ PDFE3-SEPT-E | is taken for HK_T  Configure PDFE3 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard)      |

| 20 | cGetSingle | 01001100                                                                                                          | The response contains the counter value corresponding to the PDFE0, main channel. At the same time is made the selection of PDFE0 coincidence channel for single counter next record. |

| 21 | cClearIrq  | 01110000                                                                                                          | Interrupt register                                                                                                                                                                    |

#### Calib 2

Same as Calib 1 except for step 20 which corresponds to the command 01001001: selection of single counter for PDFE1, main channel and read of single counter corresponding to PDFE0 coincidence channel.

#### Calib 3

Same as Calib 1 except for step 20 which corresponds to the command 01001101: selection single counter for PDFE1, coincidence channel and read of single counter corresponding to PDFE1, main channel

# Calib 4

Same as Calib 1 except for step 20 which corresponds to the command 01001010: selection of the single counter for PDFE2, main channel and read of single counter for PDFE1, coincidence channel

# Calib 5

Same as Calib 1 except for step 20 which corresponds to the command 01001110: selection of the single counter for the PDFE2, coincidence channel and read of single counter for the PDFE2 main channel

# Calib 6

Same as Calib 1 except for step 20 which corresponds to the command 01001011: selection of the single counter for the PDFE3, main channel and read of single counter for PDFE2 coincidence channel

#### Calib 7

Same as Calib 1 except for step 20 which corresponds to the command 0100111: selection of the single counter for the PDFE3, coincidence channel and read of single counter for PDFE3 main channel.

## Calib 8

Same as Calib 1 except for step 20 which corresponds to the command 0100000: selection of the single counter for PDFE0, main channel and read of single counter for PDFE3 coincidence channel

# **Table 10 Calibration mode sequence**

With respect to the nominal mode only the three first bits of the first byte for steps 10, 13, 16 and 19 are different: 100 in nominal mode, 101 in calibration mode.

The timing described in paragraph 8.5.2 also applies to the calibration mode.

#### 8.7 Test Generator Mode

In this mode the test generator located in the electronics produces charge pulses (frequency 17.543 kHz) that can be routed to the different PDFE inputs (main or guard). Four different

charge amplitudes (equally spread over the full range) can be generated. Each telescope has its own test generator circuitry but both circuitries are operated in parallel. This mode can only be used whenever the two telescopes are operational.

The mode is divided in two parts:

- part Test1: the configuration of the PDFEs and FPGA is similar to the nominal mode (full anticoincidence)

- part Test2: the configuration of the PDFEs and FPGA is similar to the calibration mode (coincidence with pair center segment and anticoincidence with guard ring and pair guard ring).

For each part the relevant stimuli patterns are tested and a specific channel is selected for the single counter.

The two following tables show the different configurations for both parts.

| Series<br>T1 | Pattern             | Evaluate 32-bin event counters | Evaluate single counter |

|--------------|---------------------|--------------------------------|-------------------------|

| Test1a       | CS Even alone       | CS0, CS2 (CS1, CS3)            | CS0                     |

| Test1b       | CS Odd alone        | CS1, CS3 (CS0, CS2)            | CS1                     |

| Test1c       | CS Even and CS Odd  | CS0, CS1, CS2, CS3             | CS2                     |

| Test1d       | CS Even and GR Even | CS0, CS2 (CS1, CS3)            | GR0                     |

| Test1e       | CS Odd and GR Odd   | CS1, CS3 (CS0, CS2)            | GR1                     |

| Test1f       | CS Even and GR Odd  | CS0, CS2 (CS1, CS3)            | GR3                     |

| Test1g       | CS Odd and GR Even  | CS1, CS3 (CS0, CS2)            | GR2                     |

Table 11 Test generator mode: test 1

| Series<br>T2 | Pattern                        | Evaluate 32-bin event counters | Evaluate single counter |

|--------------|--------------------------------|--------------------------------|-------------------------|

| Test2a       | CS Even and CS Odd             | CS0, CS1, CS2, CS3             | CS3                     |

| Test2b       | CS Even and CS Odd and GR Even | CS0, CS1, CS2, CS3             | GR0                     |

| Test2c       | CS Even and CS Odd and GR Odd  | CS0, CS1, CS2, CS3             | GR3                     |

Table 12 Test generator mode: test 2

Each series Test### will be repeated for four different amplitudes. Consequently the duration of the full modes is: 7 \* 4 (T1) + 3 \*4 (T2)= 40 minutes

An abbreviated test generator mode shall run with only one amplitude (duration 10 minutes). During this mode, temperature and leakage currents will be available at the same rate as for the nominal mode, ie, on a minute basis. The stimulation pattern should be recorded in the status word defined in section 10.

The timing described in paragraph 8.5.2 also applies to the test generator mode.

The test generator mode will be used once every month or less often.

The following sequence of commands details the test1a series (which should be started after the test generator test 1 configuration sequence described in paragraph 9.5). The following series of test 1 can be deduced using the Table 11 and RD1 (bits to change are color highlighted).

| Test1a |               |                                                                                                                                   |                                                                                                          |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| step   | Command       | Bit pattern +arguments                                                                                                            | Response (+ received command)                                                                            |

| 1      | cStartRun     | 01100101                                                                                                                          |                                                                                                          |

| 2      | cClearIrq con |                                                                                                                                   | E. During this period, SEP send the register (to check for latchup and                                   |

| 3      | cClearIrq     |                                                                                                                                   | Interrupt register with Bit 2 set to 1= timer interrupt                                                  |

| 4      | Cread32       | 10110000                                                                                                                          | PDFE 0 32 counters                                                                                       |

| 5      | Cread32       | 10110001                                                                                                                          | PDFE 1 32 counters                                                                                       |

| 6      | Cread32       | 10110010                                                                                                                          | PDFE 2 32 counters                                                                                       |

| 7      | Cread32       | 10110011                                                                                                                          | PDFE 3 32 counters                                                                                       |

| 8      | cConfPDFE     | 10010000+First byte:110xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ PDFE0-SEPT-E Third byte: CL_ PDFE0- SEPT-E                   | Configure PDFE0 in ADC mode                                                                              |

| 9      | cGetHK        | 01000000                                                                                                                          | HK_CS0 (1 byte), HK_GR0 (1 byte), HK_CS1 (1 byte), HK_GR1 (1 byte)                                       |

| 10     | cConfPDFE     | 10010000+First<br>byte:100xxxxx (xxxxx=<br>G_PDFE0-SEPT-E<br>Second byte: ML_<br>PDFE0-SEPT-E<br>Third byte: CL_ PDFE0-<br>SEPT-E | Configure PDFE0 back in charge amplification mode with active coincidence channel (full anticoincidence) |

| 11     | cConfPDFE     | 10010001+First byte:110xxxxx (xxxxx= G_PDFE1-SEPT-E Second byte: ML_ PDFE1-SEPT-E Third byte: CL_ PDFE1- SEPT-E                   | Configure PDFE1 in ADC mode                                                                              |

| 12     | cGetHK        | 01000001                                                                                                                          | The temperature TA is read (4 times the same values), only one is taken for HK_T                         |

| 13     | cConfPDFE     | 10010001+First byte:100xxxxx (xxxxx= G_ PDFE1-SEPT-E Second byte: ML_ PDFE1-SEPT-E Third byte: CL_ PDFE1- SEPT-E                  | Configure PDFE1 back in charge amplification mode with active coincidence channel (full anticoincidence) |

| 14     | cConfPDFE     | 10010010+First byte:110xxxxx (xxxxx= G_PDFE2-SEPT-E Second byte: ML_ PDFE2-SEPT-E Third byte: CL_ PDFE2-                          | Configure PDFE2 in ADC mode                                                                              |

|    |            | SEPT-E                                                                                                                               |                                                                                                                                                                                |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | cGetHK     | 01000010                                                                                                                             | HK_CS2 (1 byte), HK_GR2 (1 byte), HK_CS3 (1 byte), HK_GR3 (1 byte)                                                                                                             |

| 16 | cConfPDFE  | 10010001+First byte:100xxxxx (xxxxx= G_PDFE2-SEPT-E Second byte: ML_ PDFE2-SEPT-E Third byte: CL_ PDFE2- SEPT-E                      | Configure PDFE2 back in charge amplification mode with active coincidence channel (full anticoincidence)                                                                       |

| 17 | cConfPDFE  | 10010011+ First byte:<br>110xxxxx (xxxxx= G_<br>PDFE3-SEPT-E<br>Second byte: ML_<br>PDFE3-SEPT-E<br>Third byte: CL_ PDFE3-<br>SEPT-E | Configure PDFE3 in ADC mode                                                                                                                                                    |

| 18 | cGetHK     | 01000011                                                                                                                             | The temperature TB is read (4 times the same values), only one is taken for HK_T                                                                                               |

| 19 | cConfPDFE  | 10010011+ First byte:<br>100xxxxx (xxxxx= G_<br>PDFE3-SEPT-E<br>Second byte: ML_<br>PDFE3-SEPT-E<br>Third byte: CL_ PDFE3-<br>SEPT-E | Configure PDFE3 back in charge amplification mode with active coincidence channel (full anticoincidence)                                                                       |

| 20 | cGetSingle | 01001000                                                                                                                             | The response contains the counter value corresponding to the PDFE0, main channel. At the same time is made the selection of PDFE0 main channel for single counter next record. |

| 21 | cConfCal   | 1110000+ 00011000                                                                                                                    | CS0 and CS2 are stimulated with amplitude 2.                                                                                                                                   |

| 22 | cClearIrq  | 01110000                                                                                                                             | Interrupt register                                                                                                                                                             |

Test1a steps are repeated 3 more times:

- first time: step 21 is 1110000+ 00101000 (CS0 and CS2 are stimulated with amplitude 3)

- second time: step 21 is 1110000+ 00111000 (CS0 and CS2 are stimulated with amplitude 4)

- third time: step 20 is 01001001 (reading of the counter value corresponding to the PDFE0 main channel and selection of PDFE1 main channel for single counter next record. Step 21 is 1110000+00000010 (CS1 and CS3 are stimulated with amplitude 1)

Figure 5 Test1a command sequence

After test1 has been completed the configuration sequence for test2 should been carried out (see paragraph 9.5).

The following sequence of commands details the test2a series. Test2b and test 2c can be deduced using the Table 12 and RD1 (bits to change are color highlighted).

| Test2a |               |                                                                                                                 |                                                                                                                                                               |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| step   | Command       | Bit pattern +arguments                                                                                          | Response (+ received command)                                                                                                                                 |

| 1      | cStartRun     | 01100101                                                                                                        |                                                                                                                                                               |

| 2      | cClearing con |                                                                                                                 | E. During this period, SEP send the register (to check for latchup and                                                                                        |

| 3      | cClearIrq     | 01110000                                                                                                        | Interrupt register with Bit 2 set to 1= timer interrupt                                                                                                       |

| 4      | Cread32       | 10110000                                                                                                        | PDFE 0 32 counters                                                                                                                                            |

| 5      | Cread32       | 10110001                                                                                                        | PDFE 1 32 counters                                                                                                                                            |

| 6      | Cread32       | 10110010                                                                                                        | PDFE 2 32 counters                                                                                                                                            |

| 7      | Cread32       | 10110011                                                                                                        | PDFE 3 32 counters                                                                                                                                            |

| 8      | cConfPDFE     | 10010000+First byte:110xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ PDFE0-SEPT-E Third byte: CL_ PDFE0- SEPT-E | Configure PDFE0 in ADC mode                                                                                                                                   |

| 9      | cGetHK        | 01000000                                                                                                        | HK_CS0 (1 byte), HK_GR0 (1 byte), HK_CS1 (1 byte), HK_GR1 (1 byte)                                                                                            |

| 10     | cConfPDFE     | 10010000+First byte:101xxxxx (xxxxx= G_PDFE0-SEPT-E Second byte: ML_ PDFE0-SEPT-E Third byte: CL_ PDFE0- SEPT-E | Configure PDFE0 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard) |

| 11     | cConfPDFE     | 10010001+First byte:110xxxxx (xxxxx= G_PDFE1-SEPT-E Second byte: ML_ PDFE1-SEPT-E Third byte: CL_ PDFE1- SEPT-E | Configure PDFE1 in ADC mode                                                                                                                                   |

| 12     | cGetHK        | 01000001                                                                                                        | The temperature TA is read (4 times the same values), only one is taken for HK_T                                                                              |

| 13     | cConfPDFE     | 10010001+First byte:101xxxxx (xxxxx= G_PDFE1-SEPT-E Second byte: ML_ PDFE1-SEPT-E Third byte: CL_ PDFE1- SEPT-E | Configure PDFE1 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard) |

| 14     | cConfPDFE     | 10010010+First byte:110xxxxx (xxxxx= G_PDFE2-SEPT-E Second byte: ML_ PDFE2-SEPT-E Third byte: CL_ PDFE2-        | Configure PDFE2 in ADC mode                                                                                                                                   |

|    | 1          | SEPT-E                                                                                                                               |                                                                                                                                                                                |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | cGetHK     | 01000010                                                                                                                             | HK_CS2 (1 byte), HK_GR2 (1 byte), HK_CS3 (1 byte), HK_GR3 (1 byte)                                                                                                             |

| 16 | cConfPDFE  | 10010001+First byte:101xxxxx (xxxxx= G_PDFE2-SEPT-E Second byte: ML_ PDFE2-SEPT-E Third byte: CL_ PDFE2- SEPT-E                      | Configure PDFE2 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard)                  |

| 17 | cConfPDFE  | 10010011+ First byte:<br>110xxxxx (xxxxx= G_<br>PDFE3-SEPT-E<br>Second byte: ML_<br>PDFE3-SEPT-E<br>Third byte: CL_ PDFE3-<br>SEPT-E | Configure PDFE3 in ADC mode                                                                                                                                                    |

| 18 | cGetHK     | 01000011                                                                                                                             | The temperature TB is read (4 times the same values), only one is taken for HK_T                                                                                               |

| 19 | cConfPDFE  | 10010011+ First byte:<br>101xxxxx (xxxxx= G_<br>PDFE3-SEPT-E<br>Second byte: ML_<br>PDFE3-SEPT-E<br>Third byte: CL_ PDFE3-<br>SEPT-E | Configure PDFE3 back in charge amplification mode with active coincidence channel (coincidence with pair detector anti coincidence with guard and pair guard)                  |

| 20 | cGetSingle | 01001010                                                                                                                             | The response contains the counter value corresponding to the PDFE3, main channel. At the same time is made the selection of PDFE3 main channel for single counter next record. |

| 21 | cConfCal   | 1110000+ 00011010                                                                                                                    | CS0 and CS2 are stimulated with amplitude 2.                                                                                                                                   |

| 22 | cClearIrq  | 01110000                                                                                                                             | Interrupt register                                                                                                                                                             |

Test1a steps are repeated 3 more times:

- first time: step 21 is 1110000+ 00011010 (CS0, CS1, CS2 and CS3 are stimulated with amplitude 3)

- second time: step 21 is 1110000+ 00111010 (CS0, CS1, CS2 and CS3 are stimulated with amplitude 4)

- third time: step 20 is 01001100 (reading of the counter value corresponding to the PDFE3 main channel and selection of PDFE0 coincidence channel for single counter next record. Step 21 is 1110000+00001110 (CS0, CS1, CS2, CS3, GR0 and GR2 are stimulated with amplitude 1)

Figure 6 Test2a command sequence

# 8.8 A alone mode

This mode is used when telescope B is non operating (after a latchup or in case of a definitive failure). The following table shows the different series of commands to be used (whatever the previous operational mode was). The 4 series are repeated endless until a command from ground has been sent to operate telescope B again if planned

| Aalone 1 |                        |                                                                                                                                   |                                                                                                     |  |

|----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| step     | Command                | Bit pattern +arguments                                                                                                            | Response (+ received command)                                                                       |  |

| 1        | cStartRun              | 01100100                                                                                                                          |                                                                                                     |  |

| 2        | Accumulation of events |                                                                                                                                   |                                                                                                     |  |

| 3        | cClearIrq              | 01110000                                                                                                                          | Interrupt register with Bit 2 set to 1= timer interrupt                                             |  |

| 4        | Cread32                | 10110000                                                                                                                          | PDFE 0 32 counters                                                                                  |  |

| 5        | Cread32                | 10110001                                                                                                                          | PDFE 1 32 counters                                                                                  |  |

| 6        | cConfPDFE              | 10010000+First<br>byte:110xxxxx (xxxxx=<br>G_PDFE0-SEPT-E<br>Second byte: ML_<br>PDFE0-SEPT-E<br>Third byte: CL_ PDFE0-<br>SEPT-E |                                                                                                     |  |